# Low Noise, Low Input Bias Current, Rail-to-Rail Output, JFET Dual Operational Amplifier

### **Data Sheet**

#### FEATURES

Low  $T_cV_{os}$ :  $\pm 5 \ \mu$ V/°C typical Low input bias current: 20 pA typical at  $V_{sy} = \pm 15 \ V$ Low noise 7.7 nV/ $\sqrt{Hz}$  typical at f = 1 kHz 1.2  $\mu$ V rms at 20 Hz to 20 kHz Low distortion: 0.00006%

No phase reversal Rail-to-rail output Unity-gain stable

#### **APPLICATIONS**

Instrumentation Medical instruments Multipole filters Precision current measurement Photodiode amplifiers Sensors Audio

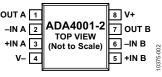

### PIN CONFIGURATION

ADA4001-2

Figure 1.8-Lead SOIC\_N (R Suffix)

#### **GENERAL DESCRIPTION**

The ADA4001-2 is a dual channel JFET amplifier that features low input voltage noise and current noise, input bias current, and rail-to-rail output.

The combination of low noise and low input bias current makes this amplifier especially suitable for high impedance sensor amplification. With low noise and fast settling times, the ADA4001-2 provides good accuracy for medical instruments, electronic measurement, and automated test equipment. Unlike many competitive amplifiers, the ADA4001-2 maintains fast settling performance even with substantial capacitive loads, and, unlike many older JFET amplifiers, the ADA4001-2 does not suffer from output phase reversal when input voltages exceed the maximum common-mode voltage range. With fast slew rate and great stability under capacitive loads, the ADA4001-2 is a good fit for filter applications. With low input bias currents and noise, it offers a wide dynamic range for photodiode amplifier circuits. Low noise and distortion, along with high output current and excellent speed, make the ADA4001-2 a great choice for audio applications.

The ADA4001-2 is specified over the -40°C to +125°C extended industrial temperature range.

The ADA4001-2 is available in an 8-lead narrow SOIC package.

Rev. C

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features 1                 | 1 |

|----------------------------|---|

| Applications               | 1 |

| Pin Configuration          | 1 |

| General Description        | 1 |

| Revision History           | 2 |

| Specifications             | 3 |

| Electrical Characteristics | 3 |

| Absolute Maximum Ratings   | 4 |

| Thermal Resistance         | 4 |

| ESD Caution                | 4 |

#### **REVISION HISTORY**

#### 5/13—Rev. B to Rev C

| Changes to Photodiode Circuits Section                    |

|-----------------------------------------------------------|

| 5/12—Rev. A to Rev B                                      |

| Changes to General Description Section                    |

| Changed Input Impedance to Input Capacitance Throughout 3 |

| Added Input Resistance Parameter, Table 1                 |

| Change to Figure 5 Caption                                |

| 2/12—Rev. 0 to Rev. A                                     |

| Changes to Figure 279                                     |

| 2/12—Revision 0: Initial Version                          |

| Typical Performance Characteristics    | 5  |

|----------------------------------------|----|

| Applications Information               | 10 |

| Total Noise Including Source Resistors | 10 |

| I-V Conversion Applications            | 10 |

| Input Bias Current                     |    |

| Noise Considerations                   |    |

| Outline Dimensions                     | 12 |

| Ordering Guide                         | 12 |

### **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{SY}}$  = ±15 V,  $V_{\text{CM}}$  = 0 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

### Table 1.

| Parameter                               | Symbol                   | Test Conditions/Comments                                                   | Min              | Тур                   | Max   | Unit    |

|-----------------------------------------|--------------------------|----------------------------------------------------------------------------|------------------|-----------------------|-------|---------|

| INPUT CHARACTERISTICS                   |                          |                                                                            |                  |                       |       |         |

| Offset Voltage                          | Vos                      |                                                                            |                  | ±0.5                  | ±1.5  | mV      |

|                                         |                          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                     |                  |                       | ±2.5  | mV      |

| Offset Voltage Drift                    | $\Delta V_{os}/\Delta T$ |                                                                            |                  | ±5                    |       | µV/°C   |

| Input Bias Current                      | IB                       |                                                                            |                  | 20                    | 30    | pА      |

|                                         |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                       |                  |                       | 4     | nA      |

| Input Offset Current                    | los                      |                                                                            |                  |                       | 20    | pА      |

|                                         |                          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                     |                  |                       | 2     | nA      |

| Input Voltage Range                     |                          |                                                                            | -12.5            |                       | +12.5 | V       |

| Common-Mode Rejection Ratio             | CMRR                     | $V_{CM} = -12.5 \text{ V to } +12.5 \text{ V}$                             | 96               | 105                   |       | dB      |

|                                         |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                       | 90               |                       |       | dB      |

| Large Signal Voltage Gain               | Avo                      | $R_L = 10 \text{ k}\Omega$ , $V_0 = -13.5 \text{ V}$ to $+13.5 \text{ V}$  | 104              | 112                   |       | dB      |

|                                         |                          | $R_L = 2 \text{ k}\Omega$ , $V_O = -13.5 \text{ V}$ to $+13.5 \text{ V}$   | 104              | 112                   |       | dB      |

|                                         |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                       | 90               |                       |       | dB      |

|                                         |                          | $R_L = 600 \Omega$ , $V_O = -13.0 V$ to $+13.0 V$                          | 90               | 93                    |       | dB      |

| Input Capacitance, Differential         | Срм                      | $V_{CM} = 0 V$                                                             |                  | 3.1                   |       | pF      |

| Input Capacitance, Common-Mode          | Ссм                      | $V_{CM} = 0 V$                                                             |                  | 4.8                   |       | pF      |

| Input Resistance                        |                          | $V_{CM} = 0 V$                                                             |                  | >1 × 10 <sup>13</sup> |       | Ω       |

| OUTPUT CHARACTERISTICS                  |                          |                                                                            |                  |                       |       |         |

| Output Voltage High                     | Vон                      | $R_L = 10 k\Omega$                                                         | 14.8             |                       |       | v       |

|                                         |                          | $R_L = 2 k\Omega$                                                          | 14.5             |                       |       | V       |

|                                         |                          | $R_L = 600 \Omega$                                                         | 13.5             |                       |       | v       |

| Output Voltage Low                      | Vol                      | $R_L = 10 k\Omega$                                                         |                  |                       | -14.8 | V       |

| . 2                                     |                          | $R_L = 2 k\Omega$                                                          |                  |                       | -14.5 | v       |

|                                         |                          | $R_L = 600 \Omega$                                                         |                  |                       | -13.5 | v       |

| Short-Circuit Current                   | lsc                      |                                                                            |                  | ±50                   |       | mA      |

| POWER SUPPLY                            |                          |                                                                            |                  |                       |       |         |

| Power Supply Rejection Ratio            | PSRR                     | $V_{s} = \pm 4.5 V \text{ to } \pm 18 V$                                   | 96               | 110                   |       | dB      |

|                                         |                          | -40°C < T <sub>A</sub> < +125°C                                            | 93               |                       |       | dB      |

| Operating Voltage Range                 |                          |                                                                            | ±5               |                       | ±18   | v       |

| Supply Current/Amplifier                | Isy                      | $V_0 = 0 V$                                                                |                  | 2                     | 3     | mA      |

|                                         |                          |                                                                            |                  |                       | 4     | mA      |

| DYNAMIC PERFORMANCE                     |                          |                                                                            |                  |                       | -     |         |

| Slew Rate                               | SR                       | $R_{i} = 2 k\Omega$                                                        | ±15 <sup>1</sup> | ±25                   |       | V/µs    |

| Gain Bandwidth Product                  | GBP                      | $V_{IN} = 5 \text{ mV } p-p, R_L = 10 \text{ k}\Omega, A_V = 100$          |                  | 16.7                  |       | MHz     |

| Unity-Gain Crossover                    | UGC                      | $V_{IN} = 5 \text{ mV } p \cdot p \cdot R_L = 10 \text{ k}\Omega, A_V = 1$ |                  | 10.2                  |       | MHz     |

| Phase Margin                            | Фм                       |                                                                            |                  | 76                    |       | Degrees |

| –3 dB Closed-Loop Bandwidth             | -3 dB                    | $A_{V} = 1, V_{IN} = 5 \text{ mV p-p}$                                     |                  | 10.3                  |       | MHz     |

| Settling Time                           | ts                       | To 0.01%, 10 V step, $G = +1$                                              |                  | 1.2                   |       | μs      |

| Total Harmonic Distortion (THD) + Noise | THD + N                  | $1 \text{ kHz}, \text{G} = +1, \text{R}_{\text{L}} = 2 \text{ k}\Omega$    |                  | 0.00006               |       | μ3<br>% |

| NOISE PERFORMANCE                       |                          |                                                                            |                  | 0.00000               |       |         |

| Voltage Noise                           | e <sub>n</sub> rms       | 20 Hz to 20 kHz                                                            |                  | 1.2                   |       | μV rms  |

| Voltage Noise Density                   |                          | f = 100  Hz                                                                |                  | 8.8                   |       | nV/√Hz  |

| voltage noise Density                   | en                       | f = 1  kHz                                                                 |                  | 8.8<br>7.7            |       | nV/√Hz  |

| Current Noise Density                   | i                        | f = 1  kHz                                                                 |                  |                       |       | fA/√Hz  |

| Current Noise Density                   | İn                       | I - I KΠΖ                                                                  |                  | 3                     |       | ΙΑ/ΥΠΖ  |

<sup>1</sup> Guaranteed by design and characterization.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                            | Rating                  |

|--------------------------------------|-------------------------|

| Supply Voltage                       | ±18V                    |

| Input Voltage                        | ±Vsy                    |

| Output Short-Circuit Duration to GND | Observe derating curves |

| Storage Temperature Range            | –65°C to +150°C         |

| Operating Temperature Range          | -40°C to +125°C         |

| Junction Temperature Range           | –65°C to +150°C         |

| Lead Temperature (Soldering, 10 sec) | 300°C                   |

| Electrostatic Discharge              | 3000 V                  |

| (Human Body Model)                   |                         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

| Table  | 3 |

|--------|---|

| I ubic | - |

| Package Type        | θ <sub>JA</sub> 1 | θıc | Unit |

|---------------------|-------------------|-----|------|

| 8-Lead SOIC_N (R-8) | 130               | 45  | °C/W |

$^1\theta_{JA}$  is specified for worst-case conditions, that is,  $\theta_{JA}$  is specified for a device soldered in a circuit board for surface-mount packages.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

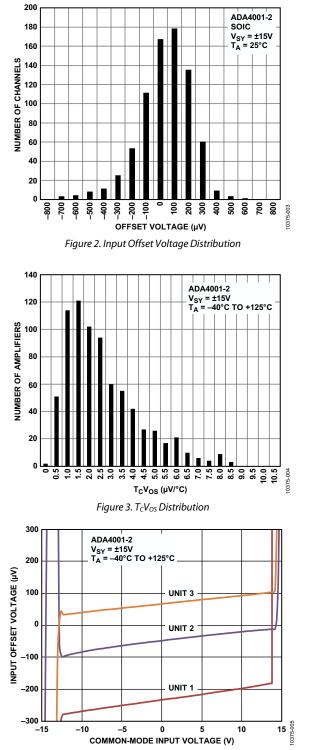

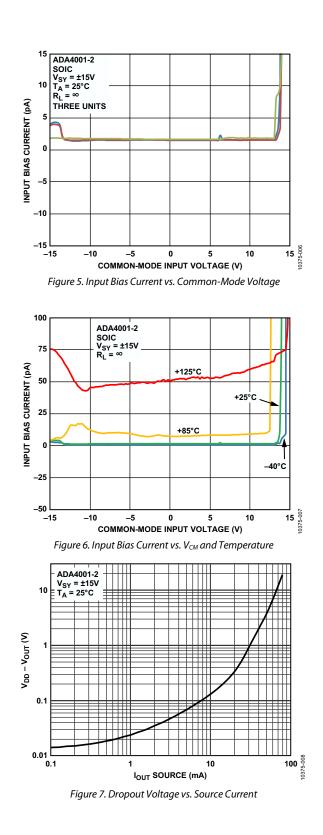

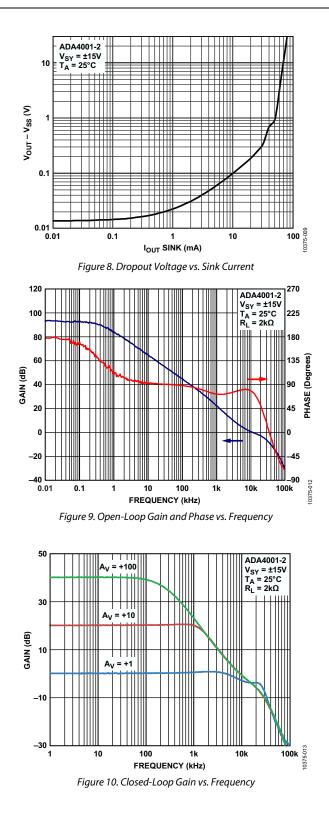

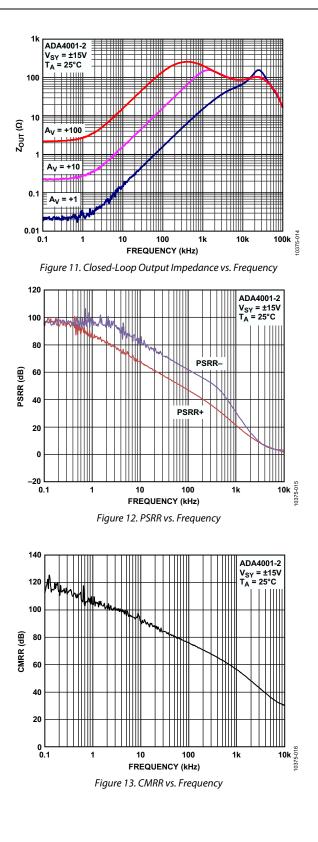

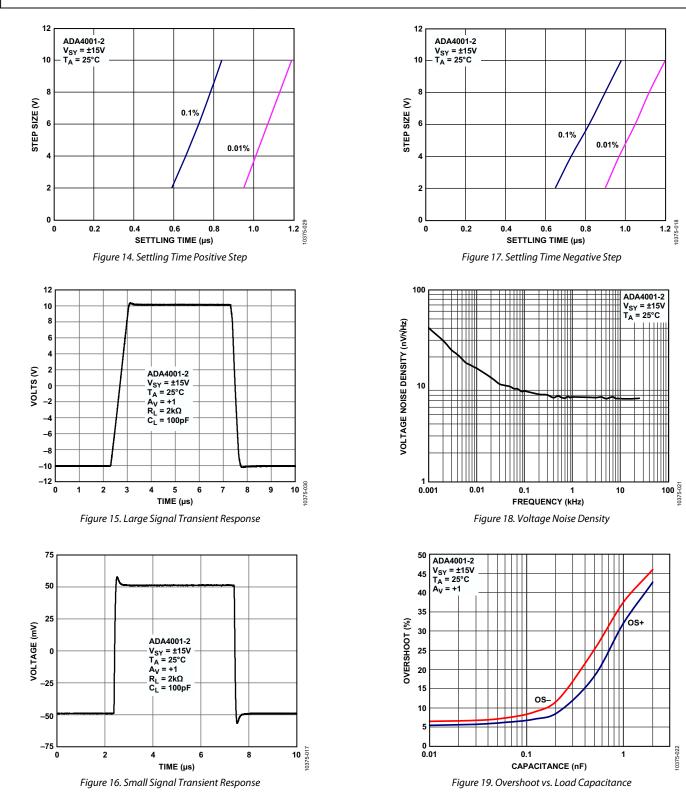

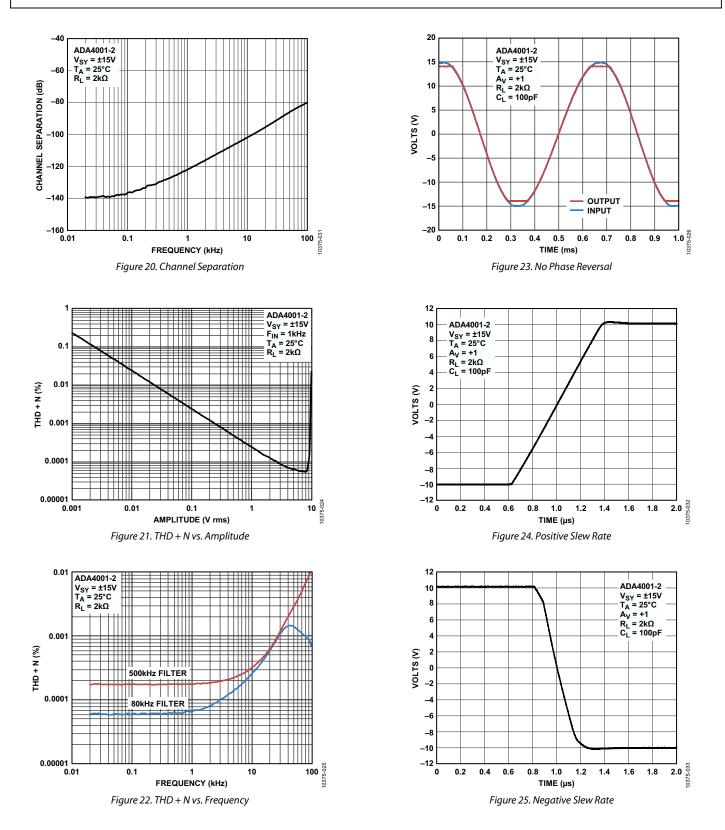

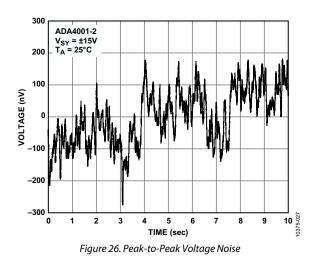

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

Figure 4. Input Offset Voltage vs. Common-Mode Voltage

### **Data Sheet**

# Data Sheet

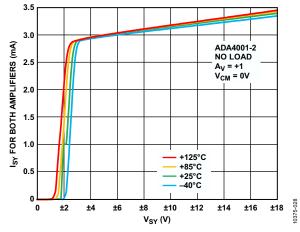

Figure 27. Supply Current vs. Supply Voltage and Temperature

### **APPLICATIONS INFORMATION** TOTAL NOISE INCLUDING SOURCE RESISTORS

The low input current noise and input bias current of the ADA4001-2 makes it the ideal amplifier for circuits with substantial input source resistance. Input offset voltage increases by less than 15 nV per 500  $\Omega$  of source resistance at room temperature. The total noise density of the circuit is

$$e_{nTOTAL}$$

$\sqrt{e_n^2}$   $(h_n R_s^2 + 44kTR_s)$

where:

$e_n$  is the input voltage noise density of the part.  $i_n$  is the input current noise density of the part.  $R_S$  is the source resistance at the noninverting terminal.

*k* is Boltzmann's constant ( $1.38 \times 10^{-23}$  J/K). *T* is the ambient temperature in Kelvin (T = 273 + °C).

For  $R_S < 4 \text{ k}\Omega$ ,  $e_n$  dominates and  $e_{nTOTAL} \approx e_n$ . The current noise of the ADA4001-2 is so low that its total density does not become a significant term unless  $R_S$  is greater than 100 M $\Omega$ , an impractical value for most applications.

The total equivalent rms noise over a specific bandwidth is expressed as

$e_{nTOTAL} = e_{nTOTAL} \sqrt{BW}$

where BW is the bandwidth in hertz.

Note that the previous analysis is valid for frequencies larger than 150 Hz and assumes flat noise above 10 kHz. For lower frequencies, flicker noise (1/f) must be considered.

#### **I-V CONVERSION APPLICATIONS**

#### **Photodiode Circuits**

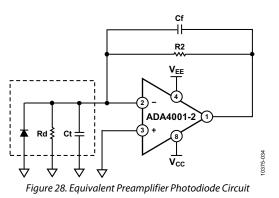

Common applications for I-V conversion include photodiode circuits where the amplifier is used to convert a current emitted by a diode placed at the negative input terminal into an output voltage.

The ADA4001-2 low input bias current, wide bandwidth, and low noise makes it an excellent choice for various photodiode applications, including fax machines, fiber optic controls, motion sensors, and bar code readers.

The circuit shown in Figure 28 uses a silicon diode with zero bias voltage. This is known as a photovoltaic mode; this configuration limits the overall noise and is suitable for instrumentation applications.

A larger signal bandwidth can be attained at the expense of additional output noise. The total input capacitance (Ct) consists of the sum of the diode capacitance and the amplifier's input capacitance (8 pF), which includes external parasitic capacitance. Ct creates a pole in the frequency response that can lead to an unstable system. To ensure stability and optimize the bandwidth of the signal, a capacitor is placed in the feedback loop of the circuit shown in Figure 28. It creates a zero and yields a bandwidth whose corner frequency is  $1/(2\pi(R2Cf))$ .

The value of R2 can be determined by the ratio

$V/I_D$

where:

V is the desired output voltage of the op amp.  $I_D$  is the diode current.

For example, if  $I_{\rm D}$  is 100  $\mu A$  and a 10 V output voltage is desired, R2 should be 100 k $\Omega$ . Rd (see Figure 28) is a junction resistance that drops typically by a factor of 2 for every 10°C increase in temperature.

A typical value for Rd is 1000 M $\Omega$ . Because Rd >> R2, the circuit behavior is not impacted by the effect of the junction resistance. The maximum signal bandwidth is

$$f_{MAX} = \sqrt{\frac{ft}{2\pi R2Ct}}$$

where *ft* is the unity gain frequency of the amplifier. Cf can be calculated by

$$Cf = \sqrt{\frac{Ct}{2\pi R^2 ft}}$$

where *ft* is the unity gain frequency of the op amp, and it achieves a phase margin,  $\varphi_M$ , of approximately 45°.

A higher phase margin can be obtained by increasing the value of Cf. Setting Cf to twice the previous value yields approximately  $\phi_M = 65^\circ$  and a maximal flat frequency response, but it reduces the maximum signal bandwidth by 50%.

#### **INPUT BIAS CURRENT**

Because the ADA4001-2 has a JFET input stage, the input bias current, due to the reverse-biased junction, has a leakage current that approximately doubles every 10°C. The power dissipation of the part, combined with the thermal resistance of the package, results in the junction temperature increasing 30°C above ambient. This parameter is tested with high speed ATE equipment, which does not result in the die temperature reaching equilibrium. This is correlated with bench measurements to match the guaranteed maximum at room temperature in Table 1.

The input current can be reduced by keeping the temperature as low as possible and using a light load on the output.

#### NOISE CONSIDERATIONS

The JFET input stage offers very low input voltage noise and input current noise. The thermal noise of a 1 k $\Omega$  resistor at room temperature is 4 nV/ $\sqrt{Hz}$ , thus low values of resistance should be used for dc-coupled inverting and noninverting amplifier configurations. In the case of transimpedance amplifiers (TIAs), current noise is more important.

The ADA4001-2 is an excellent choice for both of these applications. Analog Devices, Inc., offers a wide variety of low voltage noise and low current noise op amps in a variety of processes optimized for different supply voltage ranges. Refer to the AN-940 Application Note for a complete discussion of noise, calculations, and selection tables for more than three dozen low noise, op amp families.

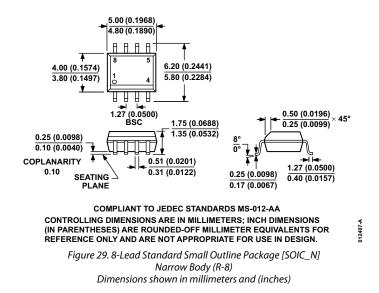

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| ADA4001-2ARZ       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |

| ADA4001-2ARZ-R7    | –40°C to +125°C   | 8-Lead SOIC_N       | R-8            |

| ADA4001-2ARZ-RL    | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |

$^{1}$  Z = RoHS Compliant Part.

www.analog.com